Vad händer egentligen inuti ett NVMe-kort vid läsning?

Du dubbelklickar på en fil och den öppnas på bråkdelen av en sekund. Det känns nästan magiskt, särskilt om du kommer ihåg hur det var med gamla hårddiskar som surrade och sökte i flera sekunder innan något hände. NVMe-kort är en av de mest dramatiska prestandaförbättringarna i modern datorteknik, men få vet vad som faktiskt sker inuti kortet under de där millisekunderna. Det handlar om elektroner, minnesceller, styrkretsar och ett protokoll designat för att hålla processorn mätt med data utan en enda onödig väntan.

Så lagras data i flashminne utan en enda rörlig del

En av de mest fascinerande aspekterna av ett NVMe-kort är att det inte innehåller ett enda rörligt mekaniskt element. Ingen roterande skiva, ingen läsarm som svänger fram och tillbaka. Ändå lagrar det gigabyte på gigabyte av data på ett sätt som överlever avstängningar, vibrationer och år av användning. Det är möjligt tack vare en teknik kallad NAND-flashminne, och för att förstå hur det fungerar behöver man börja på cellnivå.

Floating gate-transistorn som minns laddning

Den grundläggande lagringsenheten i ett NAND-flashminne är en specialdesignad transistor kallad en floating gate-transistor. Det som gör den unik är att den har ett extra lager, en flytande gate, som är helt elektriskt isolerad från omgivningen. Elektroner kan tvingas in i eller ut ur den flytande gaten genom en process kallad tunnling, där elektroner bokstavligen passerar igenom ett tunt isolerande oxidlager med hjälp av ett starkt elektriskt fält.

När elektroner är fångade i den flytande gaten förändras transistorns elektriska egenskaper på ett mätbart sätt. Det är den förändringen som representerar lagrad data. Eftersom den flytande gaten är isolerad stannar elektronerna kvar även när strömmen bryts, vilket är anledningen till att flashminne är icke-flyktigt och behåller sin data utan strömtillförsel.

Från en bit till flera: SLC, MLC, TLC och QLC

Den enklaste formen av flashminne lagrar en enda bit per cell, antingen en etta eller en nolla beroende på om elektroner är fångade i den flytande gaten eller inte. Det kallas SLC, single-level cell, och är extremt snabbt och pålitligt men också dyrt per gigabyte.

Moderna konsumentdrev använder i stället tekniker som lagrar flera bitar per cell genom att inte bara skilja mellan två tillstånd utan mellan fyra, åtta eller till och med sexton. Det görs genom att variera exakt hur många elektroner som är fångade i gaten och mäta den resulterande spänningsnivån med hög precision. TLC lagrar tre bitar per cell och är den vanligaste tekniken i konsumentdrev i dag, medan QLC lagrar fyra bitar per cell och erbjuder ännu högre densitet till priset av lägre uthållighet och något sämre prestanda vid intensiv skrivning.

Hur celler organiseras i block och sidor

Enskilda celler är organiserade i en hierarkisk struktur som är avgörande för hur läsning och skrivning fungerar. Celler grupperas i sidor, vanligtvis på 4 till 16 kilobyte, och sidor grupperas i sin tur i block som kan innehålla hundratals sidor. Läsning och skrivning sker på sidnivå, vilket är effektivt. Radering däremot måste ske på blocknivå, vilket är en av de grundläggande begränsningarna i flashminnets arkitektur och något som styrkretsen arbetar hårt för att hantera på ett sätt som inte märks i vardaglig användning.

Resan från förfrågan till data: Styrkrets och köhantering

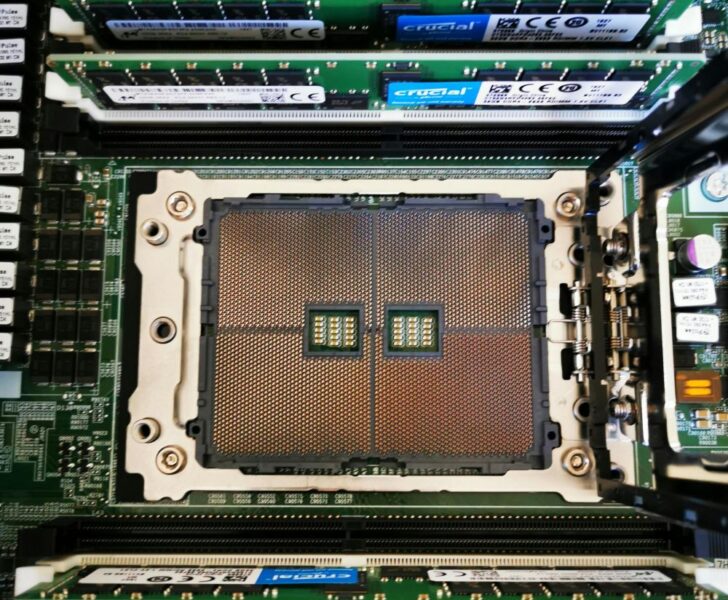

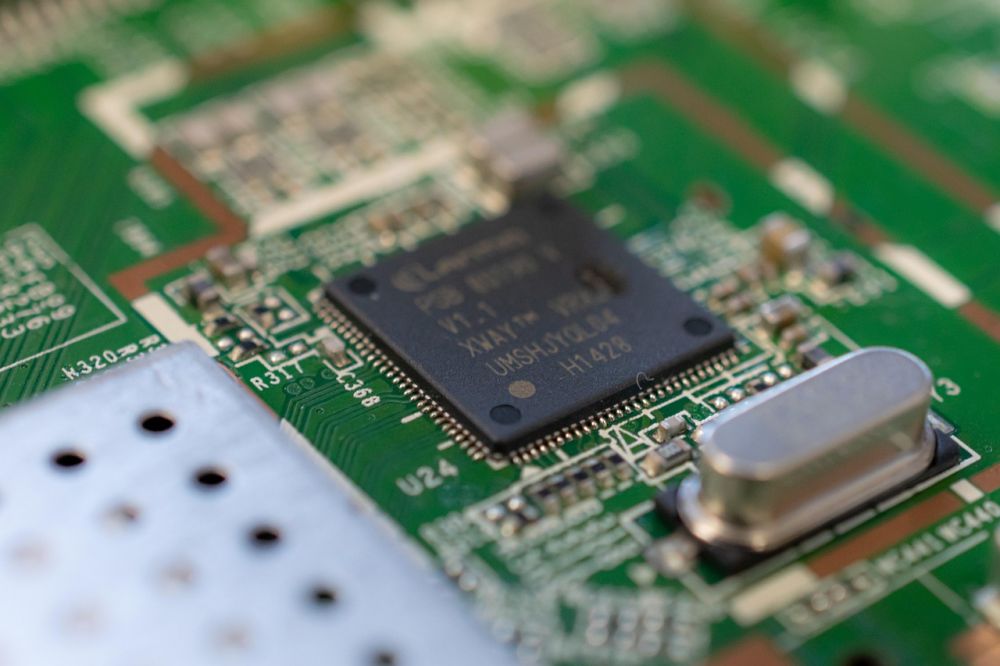

När operativsystemet ber om en fil sätts en kedja av händelser igång som sker på microsekunder. Bakom den snabbheten sitter en komponent som sällan nämns i produktspecifikationer men som är avgörande för prestandan: styrkretsen, eller controllern, som är NVMe-kortets hjärna.

Vad styrkretsen egentligen gör

Styrkretsen är ett dedikerat chip som sitter på NVMe-kortet och hanterar all kommunikation mellan värdssystemet och flashminneschipen. Den tar emot kommandon från operativsystemet via PCIe-bussen, översätter dem till operationer som flashminnet förstår och returnerar data tillbaka till processorn.

Men styrkretsen gör mycket mer än att bara vidarebefordra förfrågningar. Den håller reda på var på kortet varje bit data faktiskt lagras, vilket inte nödvändigtvis är på den plats operativsystemet tror. Det beror på en teknik kallad wear leveling, som distribuerar skrivningar jämnt över hela kortet för att förhindra att enskilda celler slits ut i förtid. Den här mappningen mellan logiska adresser, som operativsystemet ser, och fysiska adresser, där data faktiskt finns, kallas flash translation layer och underhålls kontinuerligt av styrkretsen.

Köhantering och parallellism

En av de mest betydelsefulla egenskaperna hos NVMe-protokollet är dess förmåga att hantera ett mycket stort antal samtidiga förfrågningar. Där det äldre AHCI-protokollet, som används av SATA-drev, stödjer en enda kö med maximalt 32 kommandon, stödjer NVMe upp till 65 535 köer med upp till 65 535 kommandon vardera.

Det är inte bara ett imponerande tal på papper. Det återspeglar en fundamental skillnad i hur moderna operativsystem och applikationer arbetar. I praktiken genererar ett modernt system:

- Läsförfrågningar från flera applikationer som körs parallellt

- Skrivoperationer från operativsystemets cachemekanismer

- Metadataoperationer för filsystemets underhåll

- Förhandsläsningar som operativsystemet gör i förebyggande syfte

Alla dessa förfrågningar kan nu behandlas parallellt snarare än att ställas i en enda kö och hanteras en i taget.

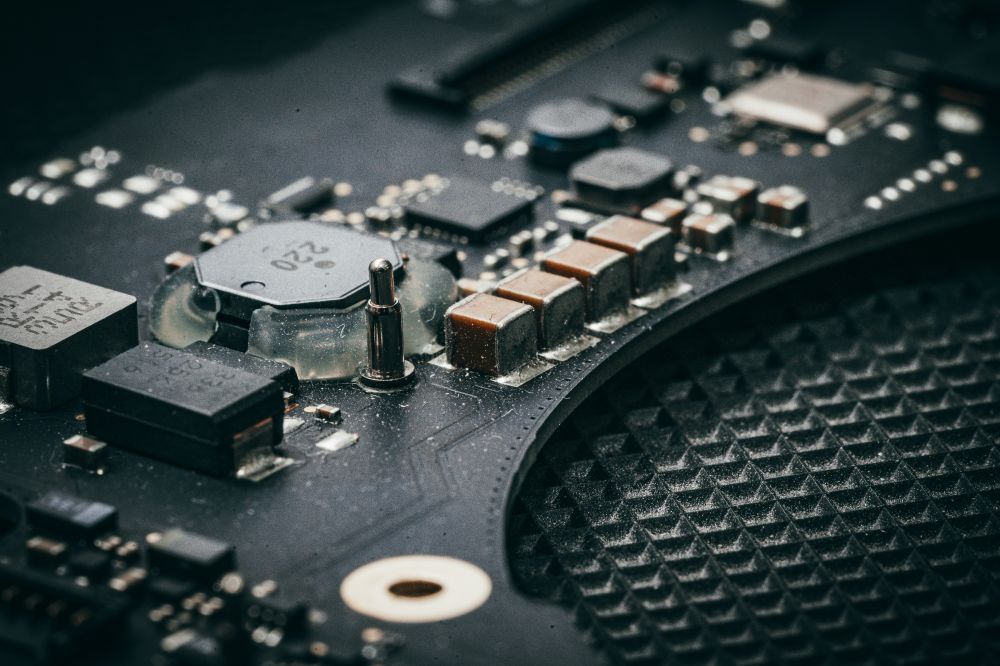

Läsbuffert och cache-hierarkin

Många NVMe-kort innehåller även ett separat DRAM-chip som fungerar som cache. Det är snabbare än flashminnet och används för att lagra flash translation layer-tabellen, som annars skulle behöva läsas från flashminnet vid varje operation, samt för att buffra data som läses eller skrivs frekvent.

När du läser en fil kontrollerar styrkretsen först om data redan finns i DRAM-cachen. Om den gör det kan den returneras nästan omedelbart. Om inte måste styrkretsen slå upp den logiska adressen i flash translation layer-tabellen, hitta rätt fysisk plats på flashminneschipen och utföra den faktiska läsoperationen.

Varför NVMe är snabbare än SATA på ett fundamentalt plan

Att NVMe-drev är snabbare än SATA-drev är välkänt, men förklaringen stannar ofta vid att NVMe använder PCIe-bussen. Det är sant men ofullständigt. Skillnaden är mer genomgripande än så och handlar om hur kommunikationen mellan lagring och processor är designad från grunden.

PCIe-bussen mot SATA-gränssnittet

SATA som gränssnitt designades ursprungligen för mekaniska hårddiskar. Hastighetstaket på 600 megabyte per sekund, som är den teoretiska maximala bandbredden för SATA 3, var generöst för en roterande disk men är en strypande flaskhals för flashminne som är kapabelt till mycket högre hastigheter.

NVMe kommunicerar direkt med processorn via PCIe-bussen, vilket är den samma buss som används av grafikkort och andra högprestandakomponenter. En PCIe 4.0-länk med fyra spår, vilket är standard för moderna NVMe-drev, erbjuder en teoretisk bandbredd på drygt 7 gigabyte per sekund i varje riktning. Det är mer än tio gånger vad SATA kan erbjuda, och PCIe 5.0 fördubblar det ytterligare.

Latens som ett arkitekturproblem

Bandbredd är en sak, men latens är minst lika viktig för upplevd prestanda. Latens är den tid som förflyter mellan att en förfrågan skickas och att de första byten av data returneras. För mekaniska hårddiskar domineras latensen av fysiska faktorer som rotationshastighet och armrörelse, typiskt i millisekunderintervallet. För SATA-baserade SSD-er är flashminnets latens låg, men protokollet och hårdvarustacken introducerar overhead.

NVMe-protokollet är designat specifikt för flashminne och har ett mycket lägre antal kommandon och en enklare kommandostruktur än AHCI. Det innebär att varje förfrågan kan behandlas med färre instruktioner och mindre overhead i styrkretsen. Typiska läslatenser för ett NVMe-drev ligger under 100 mikrosekunder, jämfört med 200 till 500 mikrosekunder för ett SATA-SSD och flera millisekunder för en mekanisk hårddisk.

Hur processorn och lagringen pratar direkt

Det kanske mest fundamentala skillnaden är att NVMe eliminerar mellanhänder. I en traditionell SATA-setup passerar data genom en AHCI-kontroller, ofta integrerad i moderkortet, innan den når processorn. Det är ett extra steg med tillhörande latens och CPU-overhead.

Med NVMe sitter drevet direkt på PCIe-bussen och kommunicerar med processorns inbyggda PCIe-kontroller utan mellanhänder. Det innebär inte bara lägre latens utan också att CPU:n kan hantera dataöverföringen mer effektivt, med stöd för avancerade tekniker som MSI-X för avbrottshantering och DMA för att flytta data direkt till systemminnet utan att belasta processorkärnorna i onödan.